Previous chapter

Internal Representaion of Instruction

거의 모든 명령어가 레지스터를 사용하므로 레지스터의 이름을 숫자로 매핑해줘야 한다.

•

$s0~$s7 : 16~23으로, $t0~$t7 : 8~15까지로 매핑한다.

add $t0, $s1, $s2

Assembly

복사

십진수 표현은 다음과 같다.

0 17 18 8 0 32

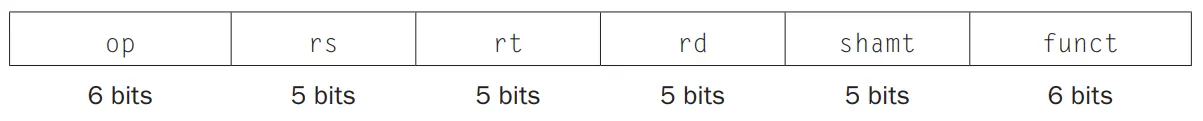

명령어의 각 부분을 필드(field)라고 부른다.

처음과 마지막 필드는 덧셈을 지시하는 필드다.

두번째는 t0, 세번째는 t1, 네번째는 t2, 다섯번째는 사용하지 않으므로 0을 사용한다.

이 명령여의 각 필드값을 바이너리 비트로 나타내면 다음과 같이 된다.

000000 10001 10010 01000 00000 100000

위 레이아웃을 명령어 형식(instruction format)이라고 한다. MIPS 인스트럭션의 길이는 데이터 워드와 마찬가지로 빠짐없이 32비트이다.

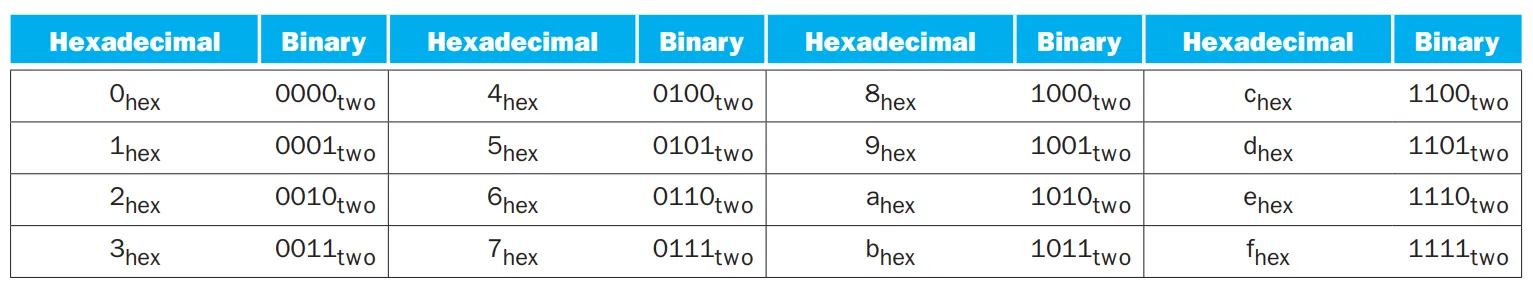

당분간 긴 이진수를 읽고 쓰는 작업이 불가피할 것으로 보이나, 모든 컴퓨터의 데이터는 4의 배수 길이이므로 Hexadecimal을 사용하여 수를 한단계 추상화할 수 있다.

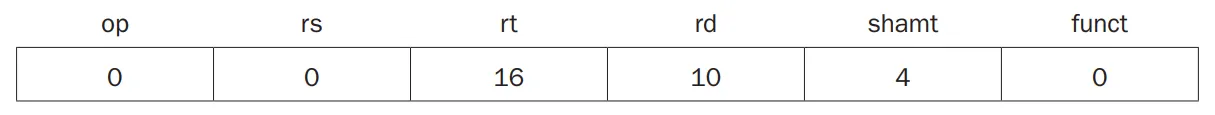

MIPS Instruction Fields

MIPS의 각 명령어의 각 필드에는 다음과 같은 이름이 붙어있다.

•

op : 명령어가 실행할 연산의 종류로서 연산자(opcode)라고 부른다.

•

rs : 첫번째 소스(source) 레지스터(register)

•

rt : 두번째 소스(source) 레지스터(register)

•

rd : 목적지(destination) 레지스터(register). 연산결과가 기억된다.

•

shamt : 자리이동량(shift).

•

funct : 기능(function). op필드에서 연산의 종류를 표시하고 funct 필드에서 한 연산을 구체적으로 지정한다.

이것보다 필드 길이가 더 길어야 할 경우 어떤 문제가 생길까?

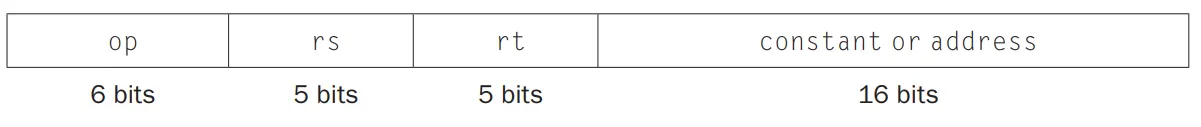

lw는 레지스터 필드 2개와 상수 필드 하나가 필요하다. 이때 접근할 수 있는 메모리는 주소로부터 최대 31까지밖에 접근할 수 없다. 5비트 필드로는 부족하다.

이런 문제 때문에 모든 명령어의 길이를 같게 하고 싶은 생각과 명령어 형식을 한가지로 통일하고 싶은 생각 사이에 충돌이 생긴다.

마지막 하드웨어 설계원칙을 슬쩍 가지고 오자.

좋은 설계에는 적당한 절충이 필요하다.

MIPS가 선택한 방향은 모든 명령어의 길이를 같게 하되, 명령어의 종류에 따라 형식을 다르게 하는 것이다.

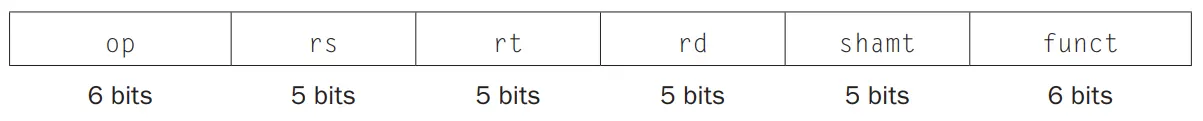

해당 방식은 R(Register)타입이라 하며, 이것만으로는 불충분하여 I타입을 만들었다.

I타입은 수치연산, 데이터 전송 명령어에서 사용되며 모양은 위와 같다.

상수나 주소가 16비트이므로 이제 lw명령은 베이스 레지스터를 기준으로 +-32768바이트만큼 지정할수 있게 된다.

lw $t0, 32($s3)

Assembly

복사

여기서 rs필드에 s3이 들어가며, rt필드에는t0, 주소필드에는 32가 들어간다.

I타입에서는 rt가 적재결과가 들어갈 목적지 레지스터 번호를 표시하는 것으로 바뀌었다.

명령어 형식이 여러개로 나뉘면 하드웨어의 복잡성이 증가하지만, 모든 형식을 비슷하게 하여 복잡도를 낮출 수 있다.

R타입과 I타입의 처음 세 필드는 이름과 크기가 같으며, I타입의 네번째 필드 길이는 R타입의 나머지 세 필드 길이를 더한 것과 같다.

명령어 타입은 첫번째 필드의 값으로 구분이 가능하다. 형식별로 op필드가 가지는 값이 다르므로 하드웨어는 op필드를 보고 명령어의 오른쪽 절반을 어떻게 해석할지 결정한다.

Logical Operator

초기 컴퓨터는 워드 전체에 대한 처리에만 관심을 가졌으나, 워드 내 일부 비트들에 대한 처리에만 관심을 가졌으나, 워드 내 일부 비트들에 대한 연산, 심지어는 개개 비트에 대한 연산도 필요하다는 것이 곧 명백해졌다.

Shift

워드 내의 모든 비트를 왼쪽 또는 오른쪽으로 이동시키고, 이동 후 빈자리는 0으로 채운다.

sll $t2, $s0, 4 #reg $t2 = reg $s0 << 4 bits

srl $t2, $s0, 4 #reg $t2 = reg $s0 >> 4 bits

Assembly

복사

시프트 연산자는 R타입 명령어이다. 특이하게도, shamt를 사용하며, rs를 사용하지 않는다.

sll 명령은 또 다른 용도로 사용될 수 있다. 왼쪽으로 i비트 자리이동하면 2^i를 곱한 것과 같은 결과가 된다.

AND OR NOT NOR

and $t0, $t1, $t2

or $t0, $t1, $t2

nor $t0, $t1, $t2

Assembly

복사

Next chapter